**LOW POWER 2 OUTPUT SYSTEM RESET IC SERIES**

#### DESCRIPTION

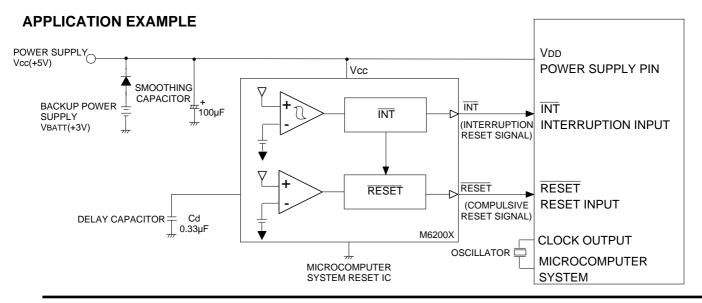

The M62001~8 are semiconductor integrated circuits whose optimum use is for the detection of the rise and fall in the power supply to a microcomputer system in order to reset or release the microcomputer system.

The M62001~8 carry out voltage detection in 2 steps and have 2 output pins. As Bi-CMOS process and low power dissipating circuits are employed, they output optimum signals through each output pin to a system that requires RAM backup, As output signals, interruption (INT) and compulsive reset(RESET) signals are available. The interruption signal(INT) is used to alter the microcomputer from normal mode to backup mode and vice versa. these output signals are classified into pulse type(M62001~M62004) and hold type (M62005~M62008).

#### **FEATURES**

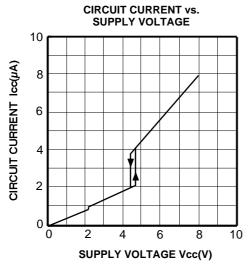

Bi-CMOS process realizes a configuration of low current dissipating circuits.

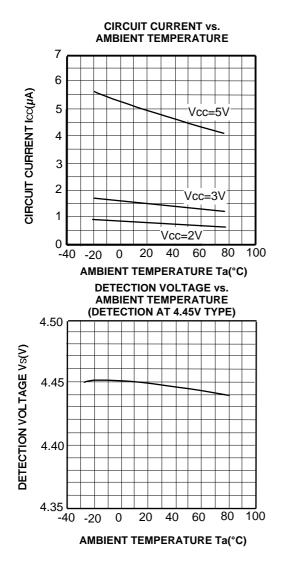

Icc=5µA(Typ.,normal mode,Vcc=5.0V) Icc=1µA(Typ.,backup mode,Vcc=2.5V)

•Two-step detection of supply voltage

Detection voltage in normal mode (2ltypes) Vs=4.45V/4.25V(Typ.)

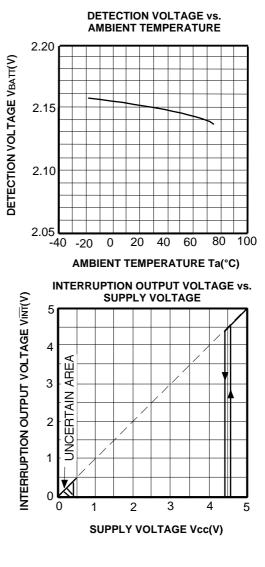

Detection voltage in backup mode VBATT=2.15V(Typ.)

•Two outputs

Reset output (RESET):Output of compulsive reset signal Interruption output(INT):Output of interruption signal

•Two types of output forms:CMOS and open drain

- •Two types of interruption output (INT) signals

Pulse type (M62001~M62004)

Hold type (M62005~M62008)

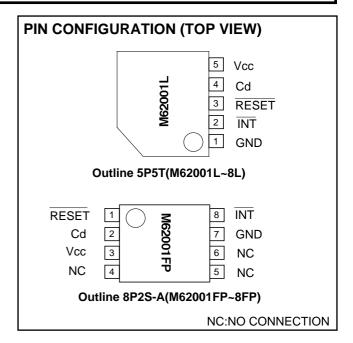

•Two types of outline packages

5-pin plastic SIP (single in-line package) 8-pin plastic SOP (mini flat package)

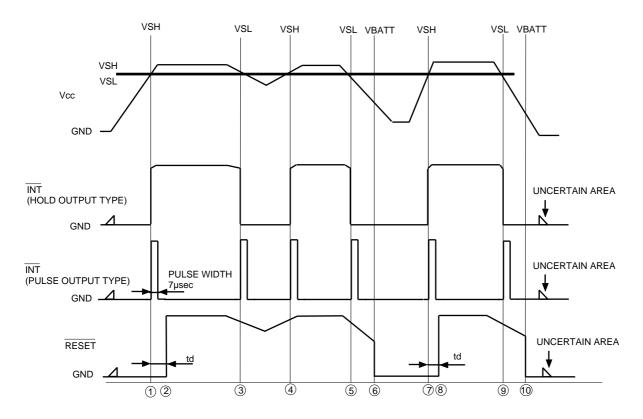

•Output based on RAM backup mode (See the timing chart.)

### **APPLICATION**

Prevention of malfunction of microcomputer systems in electronic, equipment such as OA equipment, industrial equipment, and home-use electronic appliances.

**LOW POWER 2 OUTPUT SYSTEM RESET IC SERIES**

### **ABSOLUTE MAXIMUM RATINGS**

(Ta=25°C, unless otherwise noted, These ratings commonly apply to the M62001L/FP~M62008L/FP.)

| Symbol | Parameter             | Conditions | Ratings    | Unit  |

|--------|-----------------------|------------|------------|-------|

| Vcc    | Supply voltage        |            | 8          | V     |

| ISINK  | Output sink current   |            | 5          | mA    |

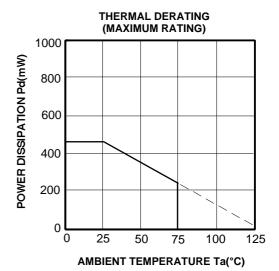

| Pd     | Power dissipation     |            | 440        | mW    |

| KΘ     | Thermal derating      | (Ta 25°C)  | 4.4        | mW/°C |

| Topr   | Operating temperature |            | -20 ~ +75  | °C    |

| Tstg   | Storage temperature   |            | -40 ~ +125 | °C    |

### **ELECTRICAL CHARACTERISTICS**

(Ta=25°C, unless otherwise noted, These ratings commonly apply to the M62001L/8L.)

| Symbol   | Parameter                      | Test conditions                                                                                                   |                                   | Limits |      |      | Unit |

|----------|--------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------|------|------|------|

| Cyrribor |                                |                                                                                                                   |                                   | Min.   | Тур. | Max. | Unit |

| Vs       | Supply voltage                 | Interruption level<br>during Vcc drop<br>(Equivalent to VsL)                                                      | (M62001,M62002,<br>M62005,M62006) | 4.30   | 4.45 | 4.60 | V    |

|          |                                |                                                                                                                   | (M62003,M62004,<br>M62007,M62008) | 4.05   | 4.25 | 4.45 |      |

| VBATT    | Battery voltage                | Reset level at backup                                                                                             | Reset level at backup             |        | 2.15 | 2.30 | V    |

| Vs       | Hysteresis voltage             | Vs=VsH-VsL                                                                                                        | Vs=VsH-VsL                        |        | 100  |      | mV   |

| laa      | Circuit current                | Vcc=5.0V:In normal mode                                                                                           |                                   |        | 5.0  | 20   | μА   |

| Icc      |                                | Vcc=2.5V:In backup mode                                                                                           |                                   |        | 1.0  | 4    |      |

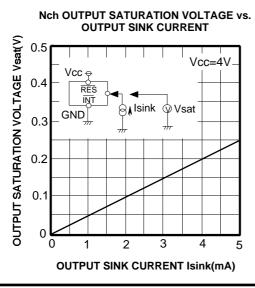

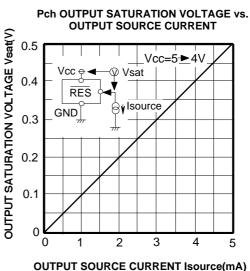

| Vsat1    | Sink ability                   | Vcc=4V,lo=4mA<br>(Output saturation voltage of N-ch transistor)                                                   |                                   |        | 0.2  | 0.4  | V    |

| Vsat2    | Source ability                 | Vcc=4V,lo=1mA<br>(Output saturation voltage of P-ch transistor:<br>[CMOS output] M62001,M62003,<br>M62005,M62007) |                                   |        | 0.2  | 0.4  | ٧    |

| td       | Delay time                     | External capacitance Cd=0.33µF                                                                                    |                                   |        | 50   |      | ms   |

| tpw      | Pulse width                    | Output pulse width (M62001,M62002,<br>M62003,M62004)                                                              |                                   |        | 7    | 10   | μS   |

| tRESET   | Reset output response time     | Time between Vcc(when falling)=VBATT and output of RESET signal                                                   |                                   |        | 30   |      | μS   |

| tīNT     | Interruption output reset time | Time between Vcc(when falling)=Vs and output of INT signal                                                        |                                   |        | 100  |      | μS   |

### SUMMARY OF M62001L/FP~M62008L/FP

| Туре   | Supply voltage detection level Vs(V) | Battery voltage detection level VBATT(V) | Output form | Interruption signal output mode |

|--------|--------------------------------------|------------------------------------------|-------------|---------------------------------|

| M62001 | 1.15                                 |                                          | CMOS        | Pulse output                    |

| M62002 | 4.45                                 |                                          | Open drain  |                                 |

| M62003 | 4.05                                 |                                          | CMOS        | ]                               |

| M62004 | 4.25                                 | 2.15                                     | Open drain  |                                 |

| M62005 | 4.45                                 | 2.10                                     | CMOS        | Hold output                     |

| M62006 | 4.45                                 |                                          | Open drain  |                                 |

| M62007 | 4.25                                 |                                          | CMOS        | ॏ <u></u>                       |

| M62008 | 4.20                                 |                                          | Open drain  | 1                               |

**LOW POWER 2 OUTPUT SYSTEM RESET IC SERIES**

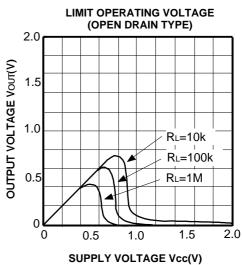

### TYPICAL CHARACTERISTICS

**LOW POWER 2 OUTPUT SYSTEM RESET IC SERIES**

**LOW POWER 2 OUTPUT SYSTEM RESET IC SERIES**

### OPERATION PRINCIPLE DESCRIPTION

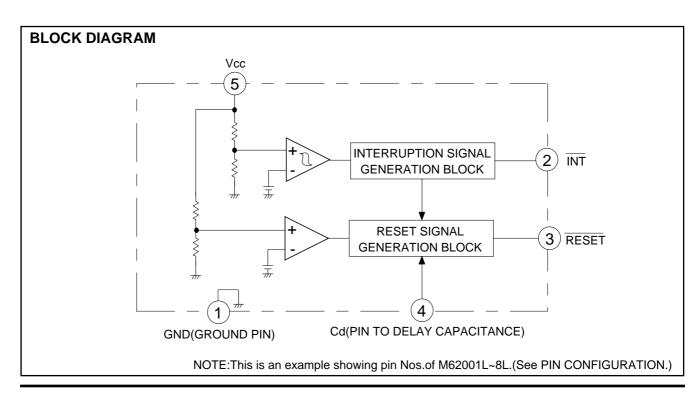

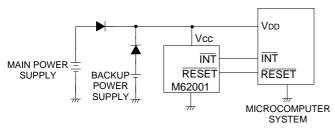

In general,the memory backup function of a microcomputer,as shown in figure,uses two diodes to switch between main power supply and backup power supply. The M62001~M62008 are ICs that,in such memory backup operation, monitor in 2 steps each voltage on the VDD line.

The ICs have an intelligent sequence such as substantial hysteresis action of RESET toward normal state at restoration of supply voltage, as well as 2-step detection in low power dissipation mode.

### **OPERATION IN DETAIL**

### 1.Two Step Detection

The ICs perform 2-step detection of supply voltage and have 2 output pins (INT and RESET). Although they have 2 comparators for 2-step detection, they differ significantly from such that are simply provided with independent detectors, because the RESET output signal is dependent at power-up and the like upon the INT output signal.

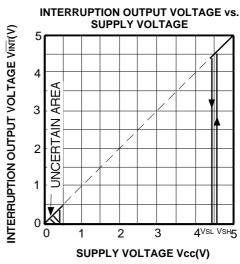

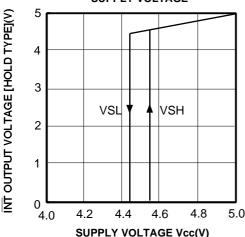

### 2.INT output (Detection of 4.45V and 4.25V)

The  $\overline{\text{INT}}$  output at the power-up of supply voltage detects VSH (4.45V/4.25V)to inform the microcomputer system of the fact that the supply voltage has reached its normal level. When the supply voltage drops from its normal level to VSL(4.45V/4.25V)an interruption signal is output to alter the microcomputer system into RAM backup mode. The microcomputer at this point enters sleep state and secures memory by a stop command issued by the interruption signal. These detection voltage ,VSH the rise,and VSL the fall,of supply voltage,have a 100-mV hysteresis voltage between themselves.

VSH-VSL=100(mV)

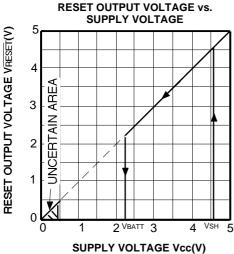

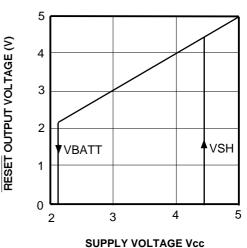

#### 3.RESET Output (Detection of 2.15V)

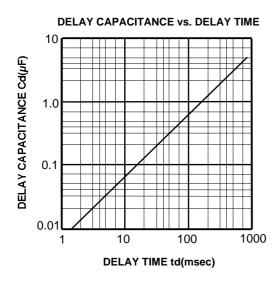

The RESET outputs a signal to prevent the microcomputer from malfunctioning due <u>to a drop</u> in supply voltage. When powering up,RESET is kept at low level until the <u>supply</u> voltage reaches VSH.If the supply voltage rises to VSH,RESET is set to high level.By inserting a capacitor between the Cd pin and GND,it is possible to produce a desired delay time (td).To set a delay time,equation below is used.

td=1.52X105 XCd(sec)

Once the supply voltage has exceeded VSH and the RESET output is set to high level, RESET maintains the high level until the supply voltage drops to VBATT. When the supply voltage drops to VBATT, RESET goes low thereby resetting and initializing the microcomputer.

The RESET output has a large hysteresis voltage of approximately 2V between the rise in supply voltage at power-up and its fall.

### RESET OUTPUT VOLTAGE VS. SUPPLY VOLTAGE

INT OUTPUT VOLTAGE VS. SUPPLY VOLTAGE

**LOW POWER 2 OUTPUT SYSTEM RESET IC SERIES**

### **OPERATION DESCRIPTION**

- 1) If Vcc rises to VSH(4.55V/4.35V), the INT output it set to high level.

- \*1.A pulse is output if INT is of pulse output type.

- (2) RESET goes high td(s) after VSH

- \*td=1.52X105XC(sec)

- (3) If Vcc drops to VSH(4.55V/4.25V), INT goes low. \*1.A pulse is output if INT is of pulse output type. \*2.The RESET output continues to be held high.

- (4) If Vcc returns to VSH, the INT output is set to high level.

- (5) Same as (3).

- (6) If Vcc becomes lower than VBATT(2.15V), the RESET output is set to low thereby resetting the microcomputer and initializing system.

- Same as (1).

- 8 Same as 2 . 9 Same as 3 and 5 .

- (10) Same as (6).